## VERSATILE ARCHITECTURES FOR ONBOARD PAYLOAD SIGNAL PROCESSING

KAREL H.G. WALTERS

#### Graduation committee

Prof. dr. ir. A.I. Mouthaan University of Twente (chairman and secretary)

Prof. dr. ir. G.I.M. Smit University of Twente (promotor)

Dr. ir. S.H. Gerez University of Twente (assistant-promotor)

Prof. dr. ir. C.H. Slump University of Twente Prof. dr. ir. P.J.M. Havinga University of Twente

Prof. dr. H. Corporaal Eindhoven University of Technology

Dr. ir. G. K. Rauwerda Recore Systems

Dr. R. Trautner **European Space Agency**

Part of this thesis was carried out under a programme

of and funded by the European Space Agency under contract no. 21986/08/NL/LvH

Massively Parallel Processor Breadboard.

The views expressed herein can in no way be taken to reflect the official opinion of the European Space Agency.

Computer Architecture for Embedded Systems Group

The Faculty of Electrical Engineering,

UNIVERSITY OF TWENTE. Mathematics and Computer Science

P.O. Box 217 7500 AE Enschede

The Netherlands.

CTIT Ph.D. Thesis Series No. 13-268

Centre for Telematics and Information Technology

P.O. Box 217

7500 AE Enschede

The Netherlands.

**፭□** Cover design by Nymus3D - www.nymus3d.nl

Printed by Gildeprint Drukkerijen - The Netherlands Typeset with LaTeX.

© Karel H.G. Walters, Enschede, the Netherlands, 2013.

Electronic mail address: k.h.g.walters@utwente.nl

ISBN 978-90-365-0850-6

ISSN 1381-3617

DOI http://dx.doi.org/10.3990/1.9789036508506

## VERSATILE ARCHITECTURES FOR ONBOARD PAYLOAD SIGNAL PROCESSING

#### DISSERTATION

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof. dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday, 9 October 2013 at 14:45

by

### Karel Hubertus Gerardus Walters

born on 8th of December 1981, in Naarden, The Netherlands

## This dissertation is approved by

Prof. dr. ir. G.J.M Smit University of Twente (promotor)

Dr. ir. S.H. Gerez University of Twente (assistant-promotor)

## **Abstract**

This thesis describes a system-on-chip (SoC) architecture for future space missions. The SoC market for deep-space missions develops slowly and is limited in features compared to the market of consumer electronics. Where consumers often cannot keep up with the features which are offered to them and sometimes even question the need for some of the options that electronics offer them, computer architectures for deep-space missions should fulfill different needs. Space is a harsh environment which requires SoCs to be shielded from radiation by hardening techniques. The missions often have a very long life-cycle: it can take more than fifteen years from the early planning stages to decommissioning of a satellite platform. The harsh environment, long lifetime and no possibility to change the hardware after launch together with the fact that mass and energy are constrained make architecture development for space more challenging than for consumer electronics.

The need for a new SoC for on-board payload processing is high. The reason is mainly due to the increased quantity of data from sensors. More sensors are mounted on board of satellites and the sensors themselves produce larger volumes of data. The bandwidth, however, to send this data back to Earth is limited. To cope with the increase in data and limitation of bandwidth, the satellite platforms need to have more processing power for distilling the information from the sensor data and compress this information sufficiently. Information distillation and compression are driving forces for algorithm development and these algorithms need to run on on-board processing platforms. Of course, algorithm development and platform development are related: algorithm development pushes platform development further while limitations of the platforms often hold back the capabilities of algorithms. This relation is explored in this thesis and from this, requirements in terms of processing power, scalability and power consumption are derived to develop a payload processing platform.

One topic of discussion related to processing platforms is often the need for hardware floating-point. This discussion is more prevalent for on-board payload processing where architecture developers want to keep the processing platform as lean as possible. Arguments in favor of small area, low power and low design complexity normally prevent inclusion of floating-point hardware in space platforms. To overcome these arguments, part of the research reported in this thesis has focused on a light-weight floating point unit.

Another difficulty for European missions is the fact that most architectures are developed based around technology from the United States of America. The USA, however, has very strict export regulations regarding technology that potentially could be used for military purposes. Although the research done by the European Space Agency is strictly for civilian purposes, this needs to be proven each time that technology from the USA is procured.

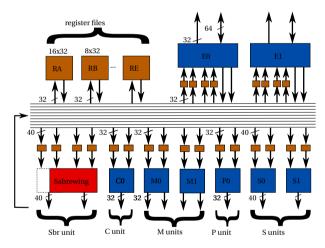

This thesis presents a hardware fused-multiply-add floating point unit, called Sabrewing, which has properties that satisfy the needs for payload processing units. Sabrewing is BSD licensed and made in Europe such that it bypasses the export regulations of the USA. It combines floating-point and fixed-point operations such that the re-use of silicon area is increased. Fusing the multiply and add stage increases accuracy and processing speed. The number of pipeline stages is only three which makes it easier to cope with in compilers and makes the design itself less complex. The design itself is small, 0.03 mm² in low power ST65nm technology, and consumes very little power: 13mW at 200Mhz for floating-point multiply-add operations. The low-power ST65nm library characteristics transfer well to a library currently under development by ST which is completely radiation hardened.

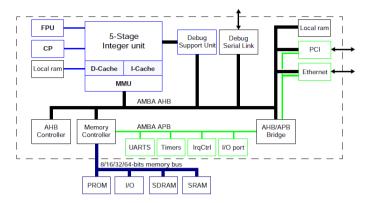

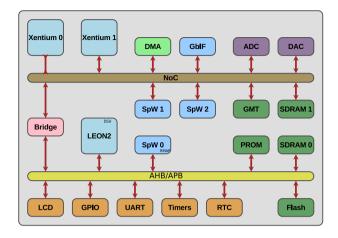

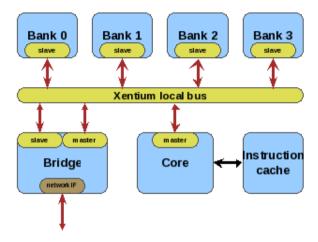

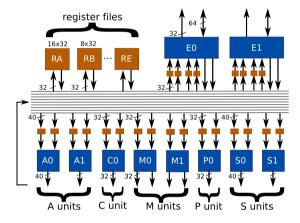

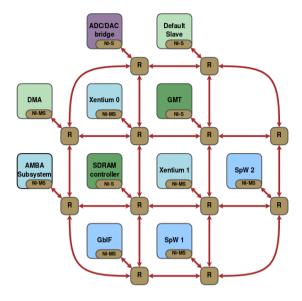

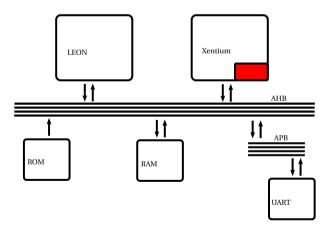

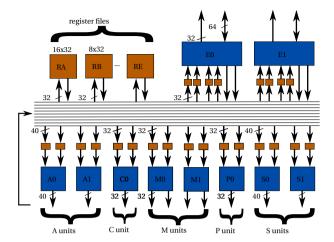

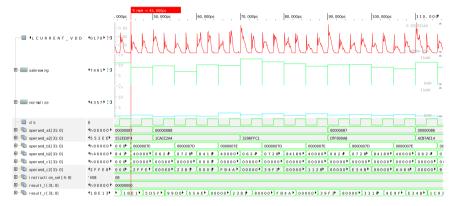

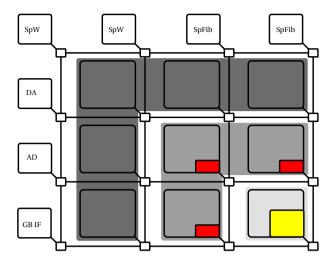

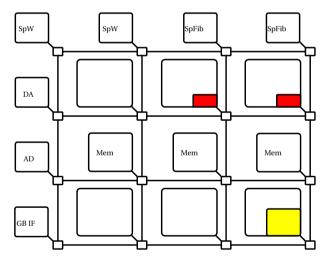

In parallel to the development of the Sabrewing, a prototype platform has been developed to increase processing capabilities for on-board payload data processing. Development of this platform could not wait until the moment that Sabrewing became available as the evaluation of all other features of the platform as presented below could not be postponed. The platform is based on the trends which can also be observed in the more conventional SoC market. It consists of two VLIW processors, Xentiums, connected to a high speed network-on-chip (NoC), in combination with distributed memories, and highspeed interfaces. To satisfy requirements for space-based platforms, standard interfaces like Spacewire are connected directly to the NoC. The NoC also has direct interfaces to high-speed AD and DA converters. Since most software for space has not been developed with multi-tile and multi-cores in mind, the NoC is connected to a more conventional system, an AMBA bus. The bus system serves as an interconnect for a LEON2 processor to run legacy software and connects a real-time clock and other payload processing oriented interfaces. The whole system is prototyped on an FPGA and can be used to test and develop new algorithms, as such serving as a testbed to develop an ASIC for deep-space missions. Several benchmarks, representative for on-board processing, have been completely implemented and show that the new platform can serve as a starting point for further development.

So, a platform based on Xentiums turns out to satisfy many of the requirements set for future space missions. However, it obviously fails to meet an

important one: the incorporation of floating-point hardware. Therefore another testbed has been created, called Nectar. This testbed is based around a LEON2 that is directly connected to a modified Xentium processor which has a Sabrewing incorporated. Nectar shows that it is relatively easy to integrate Sabrewing in a modern VLIW processor and as such shows the feasibility of an on-board processing platform with hardware floating point capabilities. Furthermore, the trade-off between software floating point and hardware floating point has been evaluated in a complete system. This comparison shows that with a minimal increase in area, 15%, a decrease in power consumption of 98% can be achieved for floating-point operations. Since it is such an improvement with minimal effort and small area increase, the discussion to incorporate hardware floating becomes an easy one. The power and area downsides to hardware floating-point almost never outweigh its benefits anymore.

There is still research needed to fully satisfy the needs of an on-board payload processing platform. The final configuration of the NoC and its interfaces will depend on the requirements of the target missions and algorithms, but the scalability of the NoC makes it simpler to derive this configuration. The size of the NoC and configuration is more a constraint of the target ASIC technology than it is of the inherent capabilities of the system. Therefore, it is envisioned that future signal processing platforms, will have differentiated (VLIW) processors interconnected by a NoC of which most are suited for high speed, high throughput integer based processing and some are more suited to perform floating point operations supported by Sabrewing.

In short, this thesis shows insight into the architecture of future processing platforms such that scientists can get the most information out of an increasing amount of raw data originating from the numerous payloads for deep-space missions. The results of this thesis are used in a follow-up project of ESA in which a radiation-hardened version of a subset of the presented system-on-chip will be manufactured, intended for a deep-space mission.

## Samenvatting

In dit proefschrift wordt een nieuw system-on-chip (SoC) beschreven bedoeld voor toekomstige ruimtemissies. De markt voor SoC's voor ruimtemissies ontwikkelt zich langzaam en is beperkt vergeleken met de markt voor consumentenelektronica. Consumenten kunnen amper de functionaliteit die de huidige elektronica hun biedt bijbenen, soms kan zich men zelfs afvragen of alle functionaliteit die geboden wordt wel vereist is. Computerarchitecturen die voor ruimtemissies bedoeld zijn moeten aan hele andere eisen voldoen. De ruimte is een zware werkomgeving voor SoC's, waar ze door speciale techniek beschermd moeten worden tegen straling. De missies hebben vaak een hele lange levenscyclus; het kan eenvoudig meer dan vijftien jaar duren van de eerste planningsfase tot de ingebruikname van een satelliet. De moeilijke werkomgeving, lange levensduur, geen enkele mogelijkheid om na lancering hardware te veranderen, samen met de restricties aan massa en energieverbruik maken de ontwikkeling van computerarchitecturen voor de ruimtevaart erg uitdagend.

De noodzaak voor een nieuwe SoC voor satelliet data-processing is hoog. De achterliggende reden hiervoor is de toename van de kwaliteit van de sensoren aan boord van de satelliet. Er bevinden zich meer en meer sensoren op de satelliet en de sensoren produceren zelf meer data. De bandbreedte om al deze data naar de aarde te sturen is gelimiteerd. Om toch zoveel mogelijk data naar de aarde te sturen wordt het steeds belangrijker dat in de satelliet veel informatie uit de beschikbare data gehaald wordt en dat deze informatie zo veel mogelijk gecomprimeerd wordt. De compressie en het distilleren van informatie uit de data zijn de grote aanjagers voor de ontwikkeling van nieuwe algoritmen die aan boord van de satellieten moeten werken. Algoritmeontwikkeling en platformontwikkeling gaan hand in hand: ontwikkelaars van algoritmen zullen pleiten voor de inzet van de nieuwste platformen, maar moeten zich uiteindelijk schikken naar de beperkingen van de keuzes gemaakt door platformontwikkelaars. In dit proefschrift wordt deze relatie onderzocht en worden hieruit vereisten gedestilleerd waaraan een nieuw platform zou moeten voldoen. Hierbij wordt onder andere gekeken naar functionaliteit, snelheid, schaalbaarheid en energieverbruik.

Een onderwerp van discussie bij de ontwikkeling van een nieuw te ontwik-

kelen platform is de noodzaak van floating-point hardware. De discussie is met name van belang bij de ontwikkeling van een platform voor een satelliet waar architectuurontwikkelaars het SoC zo klein mogelijk willen houden. De eisen van de ontwikkeling zijn onder andere: een zo klein mogelijk siliciumoppervlak, zo laag mogelijk energieverbruik en een zo simpel mogelijk ontwerp. Om aan de eisen van floating-point hardware tegemoet te komen wordt in dit proefschrift een nieuwe floating-point rekeneenheid voorgesteld.

Voor Europese ruimtevaartmissies is een ander groot probleem dat de meeste architecturen gebaseerd zijn op technologie afkomstig uit de Verenigde Staten. De Verenigde Staten hebben een zware regulering op de export van technologie die gebruikt zou kunnen worden voor militaire doeleinden. Ook al gebruikt de Europese Ruimtevaart Organisatie (ESA) technologie uitsluitend voor humanitaire doeleinden, moet dit elke keer aangetoond worden wanneer er nieuwe technologie gekocht wordt in de VS.

In dit proefschrift wordt een nieuwe rekeneenheid geïntroduceerd genaamd Sabrewing. Sabrewing biedt de mogelijkheid om een fused-multiply-add operatie uit te voeren en voldoet aan de eisen die gesteld worden aan data processing aan boord van een satelliet. Sabrewing valt onder de BSD licentie en is gemaakt in Europa waardoor het niet onder de exportrestricties van de VS valt. Sabrewing combineert floating- en fixed-point operaties waardoor het nuttig gebruik van het silicium oppervlak vergroot wordt. Door de vermenigvuldiging en optelling te combineren wordt de precisie vergroot en snelheid verhoogd. De diepte van de pipeline is maar drie 'stages', waardoor compilers er eenvoudiger mee om kunnen gaan en de complexiteit laag is. Het ontwerp is klein, 0.03 mm² in low power ST65nm technologie en verbruikt maar weinig vermogen, 13mW op 200Mhz voor fused-multiply-add operaties. De karakteristieken van de lowpower ST65nm technologie vertalen goed naar een technologie t.b.v. inzet in de ruimte die momenteel bij ST in ontwikkeling is.

Tegelijkertijd met de ontwikkeling van de Sabrewing is er een prototype platform ontwikkeld om de processorcapaciteit aan boord van satellieten te vergroten. De ontwikkeling van dit platform kon niet wachten totdat de Sabrewing klaar was omdat het platform veel meer nieuwe kenmerken heeft die tijdig geëvalueerd moesten worden. Het platform is gebaseerd op de huidige trends van de meer conventionele SoC markt. Het platform bestaat uit twee VLIW processoren, Xentiums, die verbonden zijn via een network-on-chip (NoC), gecombineerd met gedistribueerd geheugen, en hogesnelheidsinterfaces. Om aan de eisen van een ruimtevaartplatform te voldoen zijn er ook interfaces als SpaceWire aanwezig, die direct verbonden zijn met het NoC. Een AD- en een DA-omzetter zijn ook direct verbonden aan het NoC. Vanwege het feit dat de meeste ruimtevaartsoftware ontwikkeld is in een periode waarin multi-tile en multi-core architecturen nog niet bestonden, is het NoC verbonden met een conventionele AMBA bus. De bus biedt ruimte aan een LEON2 processor waar

oudere software op kan draaien, een real-time klok en andere ruimtevaartgeörienteerde interfaces. Van het complete systeem is een FPGA-prototype gebouwd opdat er nieuwe en bestaande algoritmen op getest kunnen worden. Verschillende benchmarks zijn geïmplementeerd op het platform om aan te tonen dat het een goed startpunt is voor verdere ontwikkeling met uiteindelijk een ASIC als einddoel.

Het platform, gebaseerd op Xentiums, blijkt een goed startpunt te zijn dat aan de meeste eisen voor toekomstige ruimtemissies voldoet. Aan één van deze vereisten voldoet het huidige platform nog niet, en dat is de eis van 1 GFLOP. Om dit te bewerkstelligen is er een nieuw testplatform ontwikkeld, genaamd Nectar. In dit testplatform is een LEON2 direct verbonden met een aangepaste versie van de Xentium waarin een deel van de rekenhardware is vervangen door een Sabrewing. Nectar toont aan dat het relatief eenvoudig is om Sabrewing te integreren in een moderne VLIW processor en tevens dat integratie van floatingpoint hardware in een platform t.b.v. ruimtevaart haalbaar is. Mede met behulp van dit platform is ook de afweging tussen software en hardware floating-point geëvalueerd. Deze evaluatie laat zien dat met een minimale toename in siliciumoppervlakte, 15%, een afname van 98% energie kan worden verkregen voor een floating-point operatie. Aangezien deze verbetering verkregen kan worden met een minimale toename in oppervlakte en met een minimale inspanning in werk wordt de discussie om een dergelijke verbetering door te voeren een stuk eenvoudiger. De nadelen van hardware floating-point in termen van energie en oppervlak wegen op deze manier bijna nooit meer op tegen de voordelen.

Er is nog steeds onderzoek nodig om volledig aan alle vereisten te voldoen voor een platform aan boord van een satelliet. De configuratie van het platform in zijn uiteindelijke vorm hangt grotendeels van de vereisten van de missie af, maar de schaalbaarheid van het NoC maakt het eenvoudiger om op de gewenste configuratie uit te komen. De uiteindelijke maximale grootte van het NoC en de configuratie hangen meer af van de ASIC-technologie dan van de mogelijkheden van het systeem. Vanwege deze reden is te voorzien dat toekomstige signaalverwerkingsplatformen verschillende (VLIW) processoren aan boord hebben, die via een NoC zijn verbonden en waarvan de meeste processoren gebaseerd op integerhardware zijn en enkele op floating-point Sabrewing.

In het kort laat dit proefschrift zien hoe toekomstige hardware aan boord van satellieten er uit kan zien. Met deze hardware is het mogelijk voor onderzoekers om nog meer informatie te vergaren uit de ruwe data, die de verschillende sensoren, aan boord van satellieten voor verscheidene ruimtemissies opleveren. De resultaten van dit proefschrift worden inmiddels gebruikt in een project van ESA om een tegen straling beschermd signaalverwerkingsplatform te maken voor een toekomstige deep-space missie.

## **Dankwoord**

Ten eerste wil ik graag Gerard bedanken die mij de mogelijkheid bood om te promoveren bij de vakgroep CAES. Hij heeft gedurende de hele periode ondersteuning geboden en soms ongevraagde, maar toch nodige kritiek. Hij is ook diegene die er voor gezorgd heeft dat ik een geweldige tijd kon doorbrengen in het centrum van de ruimtevaart in Europa bij ESA-ESTEC.

Sabih, die mij vooral in de laatste periode ontzettend heeft geholpen met het afronden van mijn promotie. Zijn verhelderende inzichten en commentaar, hielpen mij om het geheel toch af te ronden. Ik wil hem ook vooral bedanken voor zijn grote geduld met mij. Hij heeft ook grote invloed gehad om mijn voorliefde voor digitale hardware ontwerp via zijn onderwijs.

Het is ook tijdens dit onderwijs heb ik ook Tom leren kennen, die samen met andere studenten werkte aan een project dat ik begeleidde. Tom heeft tijdens zijn master onderzoek veel betekend voor mijn promotie waar ik hem voor wil bedanken. Ook hebben we menig uur aan de computer gezeten om problemen proberen op te lossen. Het lukte niet altijd maar vaak hebben we er toch veel plezier aan beleeft.

I would also like to thank Martin, Roland, Raffaele and Håkan for the great time I had during my stay at ESA-ESTEC. This was followed by the time I was part of the ESA project which Roland supervised. I want to thank him for the guidance and trust he put in a novice when it comes to ESA projects.

Sebastién who I got to know during the ESA project who helped me whenever I ran into problems with the platform. Ook wil ik graag Recore Systems als geheel bedanken voor het beschikbaar stellen van de Xentium voor mijn onderzoek. Graag wil ik Gerard bedanken voor zijn rol in het ESA project en de mogelijkheid om mijn onderzoek uit te voeren gedurende het project. Waar bedrijfsgeheim vaak voor een probleem zou kunnen zorgen, heeft Gerard er altijd voor gezorgd dat het zou moeten gaan om oplossingen en niet om extra problemen.

Mijn kamergenoten Maurice, Vincent en in het speciaal Albert die met mij, menig weekend heeft doorgebracht op de vakgroep. We hielden elkaar scherp door de nodige en soms keiharde humor waardoor het verblijf op de vakgroep verre van een sleur was.

Verder wil ik de hele vakgroep bedanken voor de leuke tijd tijdens koffie pauzes, vakgroep-uitjes, vrijdagmiddagen en om mijn cynisme een beetje in toom te houden. In het speciaal wil ik graag Thelma, Nicole en Marlous bedanken voor hun jaren lange ondersteuning en het luisterend oor dat ze menig promovendus bieden.

Natuurlijk bedank ik mijn ouders voor het feit dat ze me altijd de mogelijkheid en ondersteuning hebben geboden om te doen en laten wat ik wil. Mede door hen heb ik het via VWO, HBO, universiteit nu tot een promotie kunnen brengen. Mijn zusje die nu zelf promoveert en toch altijd een voorbeeld is geweest om het ook maar zo goed te kunnen als zij.

Vrienden, familie en huisgenoten hebben het vaak moeten ontzien gedurende mijn studie en promotie. Computers werden niet meer gerepareerd, aan huizen werd niet meer geklust, eten werd later gekookt en bij feestjes was ik vaak de afwezige. Mijn dank is dan ook groot voor hen die desondanks hun steun boden.

Karel Walters

## **Contents**

| Ab | strac | t                                  | i  |

|----|-------|------------------------------------|----|

| Sa | menv  | ratting                            | v  |

| Da | ınkwo | oord                               | ix |

| Co | nten  | ts                                 | хi |

| 1  | Intr  | oduction                           | 1  |

|    | 1.1   | Computers in space                 | 1  |

|    | 1.2   | Missions                           | 1  |

|    | 1.3   | Sensors                            | 2  |

|    | 1.4   | Processing platform                | 2  |

|    | 1.5   | Floating point                     | 3  |

|    | 1.6   | Next generation                    | 4  |

|    | 1.7   | Problem statement                  | 4  |

|    | 1.8   | Contributions                      | 4  |

|    | 1.9   | Structure of this thesis           | 5  |

| 2  | Nun   | nber Systems for Signal Processing | 7  |

|    | 2.1   | Introduction                       | 7  |

|    | 2.2   | Number systems                     | 8  |

|    |       | 2.2.1 Integers                     | 8  |

|    |       | 2.2.2 Signed Fixed point           | 9  |

|    |       | 2.2.3 Block floating point         | 12 |

|    |       | 2.2.4 True Floating point          | 13 |

|    | 2.3   | Conclusion                         | 20 |

| 3  | Payl  | oad processing                     | 23 |

|    | 3.1   | -                                  | 23 |

|    | 3.2   | 1 2                                | 24 |

|    | 3.3   | Gaia                               | 24 |

|    | 3 4   | IIIICF                             | 25 |

|   | 3.5  | Typical | l Algorithms                                      | 29 |

|---|------|---------|---------------------------------------------------|----|

|   |      | 3.5.1   | Fast Fourier Transform                            | 29 |

|   |      | 3.5.2   | Decimation filters and FIR filters                | 30 |

|   |      | 3.5.3   | Lossless data compression                         | 31 |

|   |      | 3.5.4   | Image data compression                            | 31 |

|   |      | 3.5.5   | Hyperspectral image compression                   | 32 |

|   | 3.6  | Archite | ectures                                           | 34 |

|   |      | 3.6.1   | LEON2                                             | 35 |

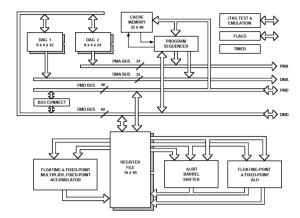

|   |      | 3.6.2   | ADSP-21020                                        | 36 |

|   |      | 3.6.3   | Actel anti-fuse                                   | 36 |

|   | 3.7  | Speed   |                                                   | 37 |

|   | 3.8  | Requir  | rements                                           | 38 |

|   | 3.9  | Possib  | le development routes                             | 40 |

|   | 3.10 | Hardw   | are floating point                                | 41 |

|   | 3.11 | Conclu  | ısion                                             | 42 |

|   |      |         |                                                   |    |

| 4 | Sabr | ewing   |                                                   | 43 |

|   | 4.1  | Introd  | uction                                            | 44 |

|   | 4.2  | Related | d Work                                            | 45 |

|   | 4.3  | Archite | ectural Design Considerations                     | 46 |

|   |      | 4.3.1   | Multiply Add                                      | 46 |

|   |      | 4.3.2   | Integer integration                               | 47 |

|   |      | 4.3.3   | Number Representation                             | 47 |

|   |      | 4.3.4   | Instructions                                      | 49 |

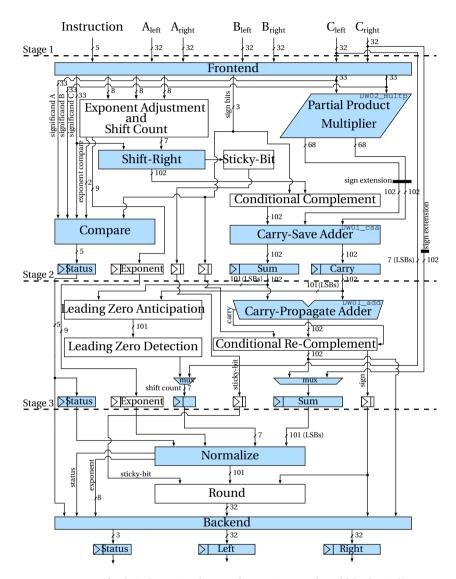

|   | 4.4  | Datapa  | ath design                                        | 49 |

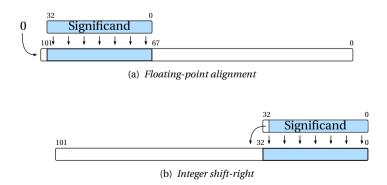

|   |      | 4.4.1   | Alignment                                         | 50 |

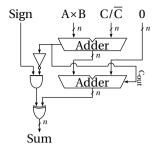

|   |      | 4.4.2   | Multiplication                                    | 51 |

|   |      | 4.4.3   | Addition                                          | 52 |

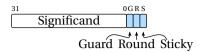

|   |      | 4.4.4   | Normalization                                     | 54 |

|   |      | 4.4.5   | Rounding                                          | 56 |

|   |      | 4.4.6   | Pipelining                                        | 56 |

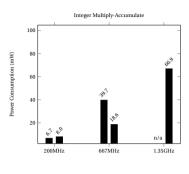

|   | 4.5  | Integer | r Operations and Floating-Point Hardware          | 56 |

|   | 4.6  | The Sa  | brewing Architecture                              | 58 |

|   | 4.7  | Realiza | ation                                             | 63 |

|   |      | 4.7.1   | FPGA                                              | 63 |

|   |      | 4.7.2   | ASIC                                              | 64 |

|   | 4.8  | Evalua  | tion                                              | 66 |

|   |      | 4.8.1   | Comparable low-power floating-point DSP solutions | 66 |

|   |      | 4.8.2   | Performance Area and Energy Comparison            | 68 |

|   |      | 4.8.3   | IEEE Compliance                                   | 68 |

|   |      | 4.8.4   | Future Work                                       | 69 |

|   | 4.9  | Conclu  | ısion                                             | 69 |

| 5  | Mas  | sively Parallel Prototyping Breadboard         | 71         |

|----|------|------------------------------------------------|------------|

|    | 5.1  | Introduction                                   | 71         |

|    | 5.2  | Prototype Platform                             | 72         |

|    |      | 5.2.1 Processing                               | 74         |

|    |      | 5.2.2 Peripherals                              | 76         |

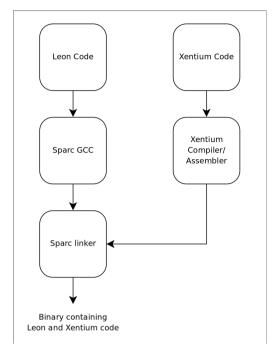

|    |      | 5.2.3 Tooling                                  | 80         |

|    |      | 5.2.4 Requirement compliance                   | 81         |

|    | 5.3  | Benchmarks                                     | 82         |

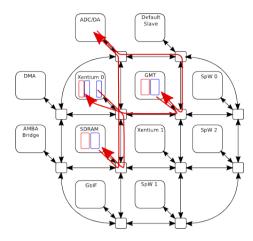

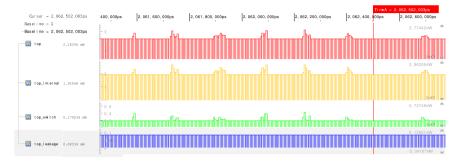

|    |      | 5.3.1 ADC / DAC processing                     | 82         |

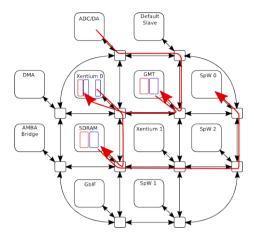

|    |      | 5.3.2 Image data compression                   | 85         |

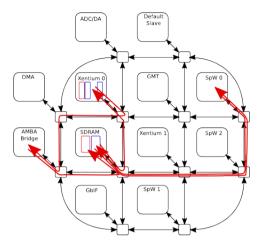

|    |      | 5.3.3 Decimation and compression               | 87         |

|    |      | 5.3.4 Demodulation and digital down conversion | 88         |

|    |      | 5.3.5 Software floating-point                  | 89         |

|    | 5.4  | Future work                                    | 91         |

|    |      | 5.4.1 Data transfers                           | 91         |

|    |      | 5.4.2 Simulator                                | 92         |

|    |      | 5.4.3 Memory                                   | 93         |

|    | 5.5  | Conclusion                                     | 93         |

| 6  | Nect | tar: Integrating Sabrewing                     | 95         |

|    | 6.1  |                                                | 95         |

|    | 6.2  | Towards an ASIC                                | 96         |

|    |      |                                                | 96         |

|    |      | 6.2.2 Giga-flops                               | 99         |

|    | 6.3  | Platform                                       | 00         |

|    | 6.4  | Integration of Sabrewing and Xentium           | 01         |

|    |      | 6.4.1 Synthesis                                | 02         |

|    |      | 6.4.2 Embedding in the Xentium software        | 107        |

|    | 6.5  | Precision                                      | 80         |

|    |      | 6.5.1 Quantization Noise for Floating-Point    | 80         |

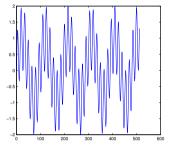

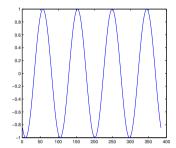

|    |      | 6.5.2 Quantization noise Experiment            | 09         |

|    |      | 6.5.3 Fused-multiply-add theory                | 10         |

|    | 6.6  | Future work                                    | 12         |

|    |      | 6.6.1 Vector operation and word length         | 12         |

|    |      | 6.6.2 SoCs for Payload Signal Processing       | 12         |

|    | 6.7  | Conclusion                                     | 13         |

| 7  | Con  | clusion                                        | 115        |

|    | 7.1  | Contribution                                   | 15         |

|    | 7.2  | Answers to research questions                  |            |

|    | 7.3  | Recommendations                                |            |

| Ar | pend | lices                                          | <b> 21</b> |

| -1 | r    |                                                |            |

| A   |        | 1                        | 23 |

|-----|--------|--------------------------|----|

|     | A.1    | Sabrewing instructions   | 23 |

| В   |        | 1                        | 25 |

|     | B.1    | Introduction             | 25 |

|     | B.2    | Compiling                | 25 |

|     | B.3    | MPPB peripherals         | 26 |

|     |        | B.3.1 LCD                | 26 |

|     |        | B.3.2 General Purpose IO | 26 |

|     |        | B.3.3 UART               | 27 |

|     |        | B.3.4 Timers             | 27 |

|     |        | B.3.5 Real-Time Clock    | 27 |

| Bil | oliogi | why 1                    | 28 |

## Chapter 1

## Introduction

#### 1.1 Computers in space

The fragility of human beings made exploration of space a field where electronics went first. It started with a series of pulses sent from the Russian Sputnik-1 satellite, which could be received all over the world. At the beginning of the space race, processing speeds were very low and data processing required huge mainframes. Early astronauts had to do calculations by hand and used slide rulers to help themselves out. The first moon landing almost failed because astronaut Buzz Aldrin wanted the landing computer to do two operations at the same time [Eyles, 2004]. Computers in space have come a long way since those days but still it is often difficult to comprehend for the general public why so much processing has to be done with so little outdated resources. Questions like, "Why has my phone more processing power than a Mars lander?" or "Why can't I directly have a live video feed of a fly-by of Jupiter?", often have to be explained in more detail to satisfy the general public.

Still, the processing done with on-board computers is primitive compared to what can be done with a current mobile phone. Small steps are being made because processing in space entails much more than just passing the sensor data to Earth for further processing. This thesis describes one such step: the architecture of a future platform for on-board processing.

#### 1.2 Missions

There are roughly three different types of the space platforms:

• *Commercial*, these are the satellites that are used in daily communication. Television, internet and telephone are services that these satellites provide.

- *Military*, these are the 'observation' satellites and other orbiting platforms which are utilized by the military branches of some countries.

- The last and possibly most interesting class, are the science-based platforms and missions.

The science-based platforms deliver amazing pictures which inspire people to look further than their own backyard. Information like the weather, and the amount of sunscreen people need to put on are provided by these platforms. Images and information from the Moon, Mars and beyond are transmitted back to Earth and provide insight into our own existence and into our past. One day they might provide answers to the question whether we are the only intelligent life form in our universe.

The science missions can also be divided roughly into two different categories. Deep-space missions and Earth-orbiting missions. The reason for this subdivide, besides the platforms mission, has to do with energy availability, radiation and mass. Closer to Earth the Earth's magnetic field shields a lot of the radiation from the Sun and outer space. That is one of the reasons why the ISS (International Space Station) is in a low-earth orbit. The Earth is relatively close to the Sun which makes solar power a good source of power. Furthermore, an orbit closer to Earth makes it possible to have a larger mass of the platform with lower costs. When traveling further away from Earth, these three factors, mass, power and radiation, start to play an increasing role.

#### 1.3 Sensors

The main reason why the amount of data to be transmitted keeps growing, are the developments in sensor technology. Cameras and other sensors are able to obtain increasingly detailed information from the outside world. This is great for scientists but difficult to deal with by engineers. The fact is that the downlink for data to Earth does not allow to send all data to Earth in real-time; the bandwidth is too small. Larger bandwidths would require more power on the platform and with it more mass. This is just not an option. For this reason, a selection on board of the satellite needs to take place on what data is required directly, how much compressions needs to be done, and what data may be delayed until there is bandwidth available.

## 1.4 Processing platform

A processing platform on board of a satellite has to take care of the collection of sensor data and has to send them back to Earth or another satellite. Currently these platforms only perform basic compression and transmit as much information as possible. Back on Earth the data is further processed and distilled into

usable information. Since the amount of sensor data increases and bandwidth to Earth practically does not, some of this processing needs to move to the satellite platform. Although the processing performance needs to increase, the demands on power, mass and radiation still hold.

Currently, processing platforms often consist of a general purpose processor in the 100Mhz range and a single or a few dedicated Application Specific Integrated Circuits (ASICs) which perform very specific tasks. Sometimes a Very Large Instruction Word (VLIW) processor is incorporated to do some more number crunching operations. Since the space environment is very demanding for the platforms and missions are relatively scarce, the platforms are often custom made. This means there is a wide variety of solutions available to suit the specific needs of a certain mission. Custom designs also make the missions very expensive and difficult to re-use for other missions because of the specific implementations. Scalable designs, which are more common in the consumer-electronics market, are often not done because each mission is very specific in nature.

Another difficulty with the designs is the long time that they need to be supported. From planning to launch takes several years and from launch to actually decommissioning of the platform can take more than a decade. Commercial-off-the-shelf hardware is just not built to be supported for those long periods and not up to the scrutiny that space hardware requires. Hardware revision changes can not be done when the craft is on the launch pad. Often, massmarket consumers are more than happy to change their mobile phone every other year to be up-to-date with current fashion. This is a luxury that the space science missions do not have.

## 1.5 Floating point

The hardware in on-board processing platforms often only supports integer operations. The reason for this is the fact that these are easier to implement, smaller in silicon area and more easily run at higher clock frequencies. Hardware floating point is more complex and requires more effort to run at higher clock frequencies. Hardware floating point has made it onto several processing platforms in space but rarely in the GigaFLOP range. Standards made this a little bit easier. The standards define how rounding should be done and what ranges of values need to be supported. When implemented completely, the hardware is often relatively large and power consuming. For these reasons, it is not that common to have high performance floating point hardware on-board of a satellite. The flexibility that hardware floating point offers, however, makes it highly desirable for algorithm developers. Having the support for hardware floating point saves development time since algorithms do not need to be converted to fixed point and integer operations. For this reason, there is a desire to

have number crunching VLIWs with support for hardware floating point.

#### 1.6 Next generation

Part of the research presented in this thesis has been performed in close collaboration with the European Space Agency (ESA). ESA is actively exploring several design concepts to obtain a platform which can serve new missions over an extended period of time. Efforts are being made to increase processing speed allowing to deal with the demand from sensors and the bandwidth limitations. The preferred target is a design which can be scaled to the needs of a mission without building an entirely new platform. The platform should be capable of running algorithms developed after completion of the design. Reaching the one GFLOP range should be possible with this platform. Furthermore, it should have high-speed interfaces, and an easy to use development environment.

#### 1.7 Problem statement

This thesis deals with a computing platform which is radiation hardened, can meet the performance requirements set by ESA and still keep cost, in terms of power and mass down. The platform needs also to have high-speed interfaces, should deal with legacy code, be scalable and usable in the future.

In particular this thesis tries to seek answers to the following questions:

- How should a future DSP platform for onboard processing look like, in view of current trends of multi-core architectures, massive parallelism and new NoC interconnects?

- How can a 1 GFLOP floating-point performance be achieved, given the constraints of deep-space missions?

- How can hardware floating-point be incorporated in a VLIW architecture?

- Can all requirements be combined with scalability?

#### 1.8 Contributions

Part of this thesis has been performed within Massively Parallel Processing Breadboard (MPPB) study of ESA. This study is one of the endeavors towards a next generation on-board processing platform. Prototyped design and the implementation of the entire benchmarks done for this platform are the main contributions of Chapter 5.

Another part of this thesis deals with combined fixed-point and floating point hardware, which is named Sabrewing it is presented in Chapter 4. Sabrewing offers fused-multiply-add operations and many derivatives. It can handle the standard IEEE single precision format as well as an extended 41 bit format

5

as well as 32 bit fixed-point arithmetic. Four out of the five rounding modes that IEEE specifies can be used in both formats. The Sabrewing is small, low power and has only three pipeline stages. It is BSD licensed such that it can be used by many designers. In Chapter 6 of this thesis, it is demonstrated that it can be implemented relatively easily in a modern VLIW with minimal resource cost and effort.

The MPPB project and the design of the Sabrewing ALU show the potential for a scalable high-performance on-board processing platform.

#### 1.9 Structure of this thesis

This thesis starts with describing the most commonly used number systems in digital hardware in Chapter 2. Some of the benefits and downsides are explained. An introduction as to why some number systems are easier to implement than others is also provided in that chapter. The thesis continues with outlining some of the existing payloads and architectures used in satellites in Chapter 3. The chapter concludes with the requirements that a next generation platform should satisfy. The mixed floating and fixed point core is described in Chapter 4. An evaluation is provided based on synthesis results. The prototype MPPB platform is introduced in Chapter 5. A combination of the MPPB platform and Sabrewing as well as its performance is presented in Chapter 6. The overall conclusions are finally listed in Chapter 7.

## **Chapter 2**

# Number Systems for Signal Processing

#### **Abstract**

The existence of different number systems in digital designs offers flexibility, but at the same time requires making decisions. They are about trade-offs between the required resources and the resolution. A high resolution and dynamic range is often a requirement from an algorithmic point of view while less resolution reduces resource consumption. This is especially important for space-related applications where mass and power have a direct influence on launch costs. This chapter provides insight into the different number systems that are commonly used in digital signal processing hardware.

#### 2.1 Introduction

Development and evaluation of a new payload processing platform in the early stages often comes down to numbers. Computer architects will request numbers in terms of calculations per second and word lengths of operands from algorithm developers. These numbers then need to be matched to what is available in terms of silicon area and power budget. The amount of silicon area available will dictate how many Digital Signal Processors (DSPs) and Central Processing Units (CPUs) can be selected to meet the processing power requirement.

When a DSP is selected, there is often a clear first selection criteria. Should the DSP be able to handle floating point numbers in hardware or not. The reasoning behind this is that although floating point hardware increases flexibility, it also increases the overall resource demand of the DSP considerably. This chapter will explain some of the number systems that are used in signal processing and provide an insight into the resources they require. The following chapter will then illustrate some current payloads and how they deal with the processing requirements as well as provide an outlook on some requirements for processing demands on future space missions.

#### 2.2 Number systems

Before introducing the most common number systems in digital hardware, it is appropriate to list the common number systems that we are used to in mathematics.

- N for positive integer values e.g. 0, 1, 2...

- $\mathbb{Z}$  for negative as well as positive integer values e.g. ... 2, 1, 0, 1, 2, ...

- $\mathbb{Q}$  for fractions e.g.  $\frac{n}{m}$  where m is not zero, the rational numbers

- $\mathbb{R}$  to express all numbers along a continuous number line, e.g. values as  $\pi$  and  $\sqrt{2}$ , the irrational numbers.

In the best case scenario, these numbers would have their identical representations in computer architectures. However computer architectures are constrained in the number of bits that can be used to represent numbers. Moving  $\mathbb{N}, \mathbb{Z}, \mathbb{Q}$  and  $\mathbb{R}$  to a constrained digital system is therefore impossible because of their infinite range and precision. In DSP architectures, the integers (see section 2.2.1) and fixed-point (see section 2.2.2) datatypes are mostly used. They can be considered approximations of  $\mathbb{Z}$  and  $\mathbb{Q}$  respectively. Moving  $\mathbb{R}$  to a digital system is even more difficult to do efficiently: not only the range but also the infinite precision that is needed, is impossible to realize on a computer architecture. The floating-point number representation does not provide the full range and precision like  $\mathbb{R}$  but does try to provide a practical implementation. We will show this in section 2.2.4. Any system used in digital signal processing is therefore an approximation of the number systems that we are used to in mathematics.

#### 2.2.1 Integers

The simplest numbers that can be represented in a computer are integers. Throughout this thesis, we use the *two's complement* representation unless mentioned otherwise. Most if not all current processing elements use this as a common input and output representation. Internally sometimes deviations are used for various reasons, as shown in Chapter 4.

The number of bits or word length (WL) affects the range of numbers that can be represented. The more bits are used, the larger the *range*. Range is the term used to express the upper and lower limit of the numbers that can be expressed. In two's complement, a signed number is represented as:

bit pattern =

$$(b_{\text{WL}-1}b_{\text{WL}-2}...b_1b_0)$$

$$N = -2^{\text{WL}-1}b_{\text{WL}-1} + \sum_{k=0}^{\text{WL}-2}b_k2^k$$

(2.1)

The first bit of a two's complement representation determines the sign of the decimal representation. Therefore this bit is referred to as the *sign bit*, which is denoted as  $b_{WI,-1}$  in Equation (2.1).

As an example, 4 bits will provide a range of  $[-2^3, 2^3 - 1]$  or [-8, 7]. Notice the inequality of the absolute value of the upper and lower bound. Adding a bit, in this case to 5 bits, will increase the range to  $[-2^4, 2^4 - 1]$ . This provides a practical implementation of numbers in the set  $\mathbb{Z}$ . To calculate the number of bits to represent a number Equation (2.2) can be used. Here  $\alpha$  denotes the integer range and WL the word length.

$$\alpha = [-2^{WL-1}, 2^{WL-1} - 1] \tag{2.2}$$

Most DSPs operate on 16 and 32 bit numbers. A common addition to this are special registers in the DSP which can hold larger numbers with more bits e.g. 40 bit.

Note that representing a number  $\mathbb{N}$  from an integer system with word length WL in a number systems with word length WL + k amount to prefixing the representation of  $\mathbb{N}$  with k sign bits. This is called *sign-extension*. Reversly, if all numbers considered have k+1 identical sign bits, the k most significant bit can be removed without loss of information.

#### 2.2.2 Signed Fixed point

Where in the previous sections the representation was limited to integers, the fixed-point representation provides the ability to represent fractions. The fixed point format is a popular format used in signal processing. It consists of an integer part with a length QI, and a fractional part, with length QF, such that the word length WL equals QI + QF. The fractional part, QF, affects the *resolution*  $\epsilon$  that can be obtained:

$$\epsilon = \frac{1}{2^{QF}}$$

Resolution is a term used to express the precision of the fraction. Practically this determines the number of digits behind the fractional point, in this case the binary point.

Taking a small step back and using a similar representation as in the previous section we obtain:

bit pattern =

$$(b_{\text{QI}-1}b_{\text{QI}-2}...b_1b_0.b_{-1}b_{-2}...b_{-QF})$$

$$N = -2^{\text{QI}-1}b_{\text{QI}-1} + \sum_{k=-\text{OF}}^{\text{QI}-2}b_k2^k$$

As with the previous integer representation this representation is also two's complement in which the sign bit is now indicated by  $b_{QI-1}$ . The QI part (integer part) is split from the QF part (fractional part) by the *binary point*.

To know how many fractional bits are needed to obtain a certain resolution  $\epsilon$ , we can use the following equation (notice the ceiling operation  $\lceil \rceil$ ):

$$QF = \left\lceil \log_2\left(\frac{1}{\epsilon}\right) \right\rceil$$

If we then for example want to express a precision,  $\rho$ , of  $\rho \le 0.0001$  (decimal), the equation tells us that we need 14 bits as shown here:

$$\begin{aligned} \mathbf{QF} &= \left\lceil \log_2 \left( \frac{1}{\rho} \right) \right\rceil \\ \mathbf{QF} &= \left\lceil \log_2 \left( \frac{1}{0.0001} \right) \right\rceil \\ \mathbf{QF} &= \left\lceil \log_2 \left( 10000 \right) \right\rceil = \left\lceil 13.288 \right\rceil = 14 \end{aligned}$$

To express the fixed-point format, the notation < QI.QF > is used. For a 16-bit number in which 1 bit is used for the integer part and 15 for the fraction the notation is: < 1.15 >. Effectively the single integer bit is only used to indicate the sign of the fraction. Putting the integer range and fraction resolution together into one equation:

$$\alpha = \left[-2^{QI-1}, \left(2^{QI-1}-2^{-QF}\right)\right]$$

resolution =  $2^{-QF}$

The number of bits therefore equals WL = QI + QF. The fixed-point representation provides a practical implementation of a subset of  $\mathbb{Q}$ .

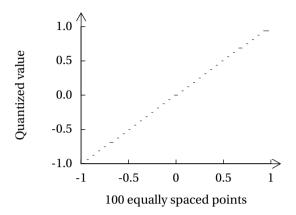

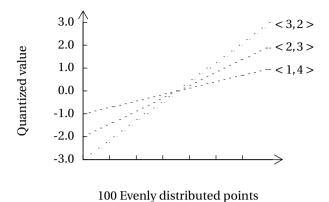

Figure 2.1 shows 100 equally spaced numbers in the -1 to 1 range in a < 1.4 > format. The limitations of this number system are clearly visible. The 100 equally space numbers are projected onto a fixed number format having a resolution of 0.02. Correct (lossless) mapping requires at least 6 bits in the fraction to represent correctly. As there are only 4 bits available, multiple numbers are mapped on the same bit-pattern. This is the *quantization* effect. Rounding explains why not all horizontal lines in Figure 2.1 have the same length.

FIGURE 2.1 – Fixed curve limitation < 1.4 > in the -1 to 1 range.

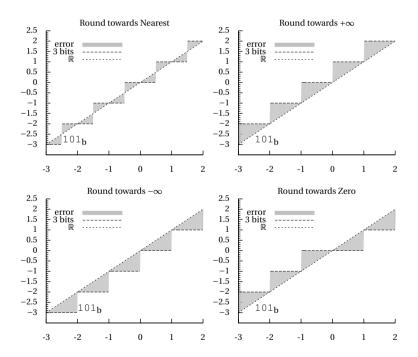

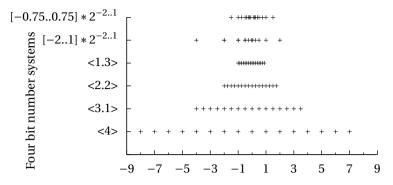

FIGURE 2.2 – Quantization examples in a 3 bit system

Quantization is the procedure in which a number is represented with less precision than the original representation and information is lost in the process. An example of quantization in the decimal system would be expressing 3.00 as 3.0. In this particular example there is no information loss and as such the quantization error is 0.00. However, if we quantize the number 3.05, to either 3.1 or 3.0 (depending on how the number is rounded), the quantization error is 0.05 or -0.05. Figure 2.2 shows examples of quantization in a 3 bit system. The diagonal line is a representation of  $\mathbb{R}$  in which every number can be represented, in this case 500 equally spaced points in the -3 to 2 range. The horizontal lines are the numbers that can be represented using the 3 bits that are available. The gray area is the difference, quantization error, between the un-quantized number and the two's complement fixed-point number. Rounding is an operation that is applied to a number to achieve quantization. It requires a conditional addition or subtraction when implemented by a computer. Quantization that amounts to merely removing bits when reducing resolution is called *truncation*. Another form is taking into account what number is "nearest" and rounding towards that, which is what happens in Figure 2.2 top-left sub-figure. The other limitation of fixed point numbers, next to the quantization effect, is the same as with the integer system; the range is limited.

The question arises: Why would we use these fixed point systems? There are two main reasons. The hardware to implement basic operations like addition, subtraction and multiplication is not complex and it requires a small amount of resources compared to an implementation that is a closer approximation of  $\mathbb{R}$ .

#### 2.2.3 Block floating point

To increase the range that can be expressed, with the same number of bits, other representations have been introduced. One of these systems is block floating point [Kalliojarvi and Astola, 1996] [Oppenheim, 1970]. The limitation of fixed point is the fact that the number of fractional bits is predetermined and as such fixed. Block floating point tries to alleviate this by keeping track of a value that represents the scaling factor for a certain number of fractions. The scaling is a power-of-two multiplication that effectively shifts the binary point. This allows the programmer to shift the binary point to allow for a larger and smaller fraction range at the cost of precision. The ability to store this value is not the only hardware feature that is required but one also needs the ability to count the leading sign bits efficiently in hardware. Counting the leading sign bits allows the programmer to obtain the scaling-factor and shift the value with the number of redundant sign bits. A number of DSPs provides this instruction. The C5000 (low power DSP series) from Texas Instruments [Texas Instruments, 2009], offers the EXP instruction which counts the leading zeros. The Blackfin series from Analog Devices [Analog Devices, 2012] offers the SIGNBIT instruction which

FIGURE 2.3 – Block curve limitation for 5 bits in three ranges

does the same thing. This means that these DSPs have the implicit possibility to work with block floating point although this is not always advertised as such.

Normally, in the fixed point format, all numbers would have a static format such as <1.4> or <2.3>, but with the extra register, the location of the binary point can be varied. The register effectively holds the value with which the stored values needs to shift to get all the values aligned; one could call this value the scaling factor. The system makes it possible to have different locations of the binary point. There are some drawbacks to this system which are made clear in Figure 2.3. Figure 2.3 shows three different fixed-point formats number representations of 5 bits. The first "curve" is in a <2.3> format, from [-2,2), the register holds a 0. The second "curve" is in a <3.2> format, from [-3,3), the register holds a 1. The third "curve" is in a <1.4> format, from [-1,1), the register holds a -1.

Although the resolution is more flexible and the ranges improve a bit, the range is still fixed for the values that are in the same block. Another drawback which is less apparent, is the increased complexity of the source code in which this system is used. The software will need to keep track of the range of values in with the same exponent as well updating the register that holds the value of the exponent. The decision on the size of the block containing the values with the same exponent as well as the exponent value is completely in the hand of the programmer.

#### 2.2.4 True Floating point

The last system we want to discuss is true *floating point*. This system is introduced to be able to approximate numbers from the set  $\mathbb R$ . In this representation the binary point has a flexible position, hence the term floating. It is almost the

Expressable numbers in different 4 bit number systems

FIGURE 2.4 - Different numbersystems with 4 bits.

same as having block floating point in which the block only holds a single value. The register that holds the exponent is then included in the representation itself. As such this system holds the exponent as well as the fraction. In floating point the fraction is often referred to as *significand* or *mantissa*. Throughout this thesis we will refer to it as the significand. The combination of significand and exponent represents the following number:

$$\pm S \times 2^e$$

Here S denotes the significand and *e* the exponent.

Since the number of bits in a word is fixed; one needs to decide how many bits are allocated to the exponent and how many to the significand. One also has different choice for the encoding of the exponent and significand (e.g. two's complicant or sign magnitude). This has been a discussion since the existence of floating point itself. Figure 2.4 shows the different possible representations of 4 bits that we have discussed sofar, as well as two floating point formats. The difference between the top two is that the first employs sign magnitude encoding for the significand and includes a so called *hidden bit*. The second uses two's complement for the significand as well as the exponent. Going further down, the three following formats are fixed-point formats which represent numbers from the  $\mathbb Q$  set. The bottom representation encodes 4-bit integers (from  $\mathbb Z$ ).

In sign-magnitude representation, there is a single bit that represents the sign of the value while the other bits represent the magnitude. This is different from two's complement in which the value after the sign-bit does not directly represent the magnitude, the difference is depicted in Table 2.1 The advantage of the sign-magnitude representation is that it is symmetrical while the two's complement representation is not. On the other hand sign-magnitude, has two

representations for zero whereas, two's complement has only one representation of zero.

| Decimal<br>Representation | Sign-Magnitude<br>Representation | Two's Complement<br>Representation |

|---------------------------|----------------------------------|------------------------------------|

| -4                        | NA                               | 100                                |

| -3                        | 111                              | 101                                |

| -2                        | 110                              | 110                                |

| -1                        | 101                              | 111                                |

| -0                        | 100                              | 000                                |

| +0                        | 000                              | 000                                |

| +1                        | 001                              | 001                                |

| +2                        | 010                              | 010                                |

| +3                        | 011                              | 011                                |

TABLE 2.1 – Sign-magnitude and two's complement representation with 3 bits.

For the top floating point representation in Figure 2.4, sign-magnitude is used for the significand part. Next to this a so called hidden bit used. The hidden bit is not part of the bit pattern since it is always set to 1. This is done to always have a so called *normalized number*.

Table 2.2 helps to explain why there is a need for normalization. The first column shows a five bit pattern in which the first two bits are the two's complement representation of the exponent and the other three bits are the sign-magnitude representation of the significand with a binary point in between. The second column shows the decimal value of this bit pattern. The third column shows the same bit pattern but with the introduction of the hidden third bit which normalizes the value, and the fourth column the decimal value corresponding with this pattern. The table shows that when the pattern is not normalized, different bit patterns represent the same decimal value which is not an efficient use of the available bits. When using a hidden bit, the significand is shifted to the left until a binary 1 is on the left most position and the exponent is modified accordingly. Since there is always a one on the left most position this bit can be discarded in the actual representation and as such become the hidden bit.

Table 2.3 depicts the floating point values of the top two rows of Figure 2.4. The first column is the decimal value that corresponds to the second column. The third column is the same binary representation as the second but now interpreted as a normalized sign-magnitude significand with a hidden bit. The fourth column is the decimal value that corresponds to the third column. What can be seen, is, that the normalization eradicates the duplicate values and makes the bit pattern more efficient.

| Not Normalized<br>Bit Pattern | Decimal<br>Representation   | Normalized<br>Bit Pattern | Decimal<br>Representation    |

|-------------------------------|-----------------------------|---------------------------|------------------------------|

| 10 0 .00                      | $2^{-2} \times 0 = 0$       | 10 0 .1 0                 | $2^{-2} \times 0.5 = 0.125$  |

| 11 0 .00                      | $2^{-1} \times 0 = 0$       | 11 0 <b>.1</b> 0          | $2^{-1} \times 0.5 = 0.25$   |

| 00 1 .10                      | $2^0 \times -0.5 = -0.5$    | 00 1 .1 0                 | $2^0 \times -0.5 = -0.5$     |

| 01 1 01                       | $2^{1} \times -0.25 = -0.5$ | 01 1 <b>1</b> 1           | $2^{1} \times -0.75 = -0.75$ |

Table 2.2 – Normalization

Still the question remains why sign-magnitude encoding is chosen for the significand. The normalization could indeed be done with two's complement but would be a bit more difficult. A second reason is the fact that the sign magnitude makes the range symmetrical. The third reason is most likely due to historical reasons, which probably has to do with the property that it is easier to visually see which binary representation is larger than the other.

Table 2.3 – Two different floating point formats: two's complement exponent and significand (ee SS) and a normalized sign-magnitude with hidden bit (ee SS h S)

| Decimal<br>Representation | Two's Complement | Normalized Sign-Magnitude<br>ee s h S | Decimal<br>Representation |

|---------------------------|------------------|---------------------------------------|---------------------------|

| -4                        | 01 10            | 01 1 <b>.1</b> 0                      | -1                        |

| -2                        | 01 11            | 01 1 <b>.1</b> 1                      | -1.5                      |

| -2                        | 00 10            | 00 1 <b>.1</b> 0                      | -0.5                      |

| -1                        | 00 11            | 00 1 <b>.1</b> 1                      | -0.75                     |

| -1                        | 11 10            | 11 1 <b>.1</b> 0                      | -0.25                     |

| -0.5                      | 10 10            | 10 1 <b>.1</b> 0                      | -0.125                    |

| -0.5                      | 11 11            | 11 1 <b>.1</b> 1                      | -0.375                    |

| -0.25                     | 10 11            | 10 1 <b>.1</b> 1                      | -0.1875                   |

| 0                         | 00 00            | 00 0.1 0                              | 0.5                       |

| 0                         | 01 00            | 01 0.1 0                              | 1                         |

| 0                         | 10 00            | 10 0 <b>.1</b> 0                      | 0.125                     |

| 0                         | 11 00            | 11 0 <b>.1</b> 0                      | 0.25                      |

| 0.25                      | 10 01            | 10 0 <b>.1</b> 1                      | 0.1875                    |

| 0.5                       | 11 01            | 11 0 <b>.1</b> 1                      | 0.375                     |

| 1                         | 00 01            | 00 0 <b>.1</b> 1                      | 0.75                      |

| 2                         | 01 01            | 01 0.1 1                              | 1.5                       |

The first computer capable of true floating point operations was the Z1, a mechanical computer from 1938 developed by Konrad Zuse [Rojas, 1997]. So, already in those days Zuse saw the need to overcome the limitations of fixed-point representations. Interoperability between different architectures was less of a problem in that era but did become a problem after more manufacturers began to produce processing architectures incorporating floating point. Manufacturers such as IBM, HP, DEC and Cray all had their proprietary floating point

formats. IBM for instance used a base 16 representation for their exponent. Cray on the other hand decided that it was best to use at least 64 bits for floating point number to reduce the chance of overflow and underflow. This situation had to change to be able to easily exchange data between the different architectures. Several companies sat down and developed a standard which became the IEEE-754 standard and later the IEEE-754-2008 standard [IEEE Task P754, 2008] which includes some updates and a decimal format.

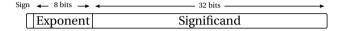

#### IEEE-754-2008

The IEEE-754-2008 standard deals with two floating point formats: the decimal and binary format. The decimal format is mainly used in the financial world where rounding errors are of greater concern than data efficiency. We will only consider the binary floating point format since we are mainly interested in compact architectures. The standard itself does not specify anything related to implementation. It describes how the operations on the floating point numbers should behave. For example it states "rounding should behave as if there is an infinite precision available". The standard does not describe how one should or can achieve this. The standard describes five basic binary formats as shown in Table 2.4. The first four formats have common word-lengths of 16,32,64 and 128. The fifth format in Table 2.4 is special. It provides the option for a custom format in which the relation between exponent and significand is fixed. In a few occasions, this is used by hardware manufacturers to allow for increased precision compared to the already defined formats.

TABLE 2.4 – Segmentation of the different formats described by IEEE-754-2008

| Precision             | <b>Significand</b> (+hidden-bit)                              | Exponent (bits)                              | Bias               |

|-----------------------|---------------------------------------------------------------|----------------------------------------------|--------------------|

| Binary                |                                                               |                                              |                    |

| half (16-bit)         | 11                                                            | 5                                            | 15                 |

| single (32-bit)       | 24                                                            | 8                                            | 127                |

| double (64-bit)       | 53                                                            | 11                                           | 1023               |

| quadruple (128-bit)   | 113                                                           | 15                                           | 16383              |

| custom (k-bit, k≥128) | $\underset{*}{\text{k}} - \text{rnd}(4 \times log_2(k)) + 13$ | $\operatorname{rnd}(4 \times log_2(k)) - 13$ | $2^{(k-s-1)}-1$ ** |

<sup>\*</sup>The rnd function rounds to the nearest integer

The exponent is in a biased form, this means that for the single precision format a *bias* of 127 is added to the exponent before it is stored in the 8 bits. The actual range for these 8 bits is thus 0-255 to obtain an exponent of -127 to 128. Zero and 255 represent special cases. There are two other terms related to a floating point number system: *ULP* and *machine epsilon*.

The ULP (Unit in the Last Place) is the maximum rounding error for a given exponent value. The ULP is the value that is presented by the last bit of the

<sup>\*\*</sup> s is the significand width.

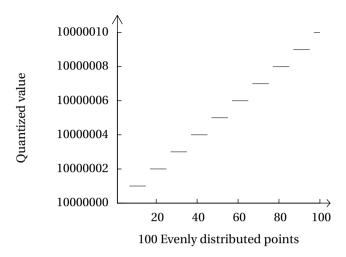

FIGURE 2.5 – Float curve limitation ULP  $\approx 1$

significand. The machine epsilon is a term coined to express the relative rounding error of a floating point number. Two values that have the same exponent and differ only the last bit of the significand are thus in 1 ULP distance of each other. The IEEE standard states that the result of an elementary mathematical operation should never be more than 0.5 ULP from the mathematically exact result.

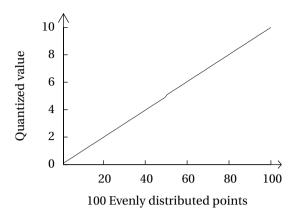

The machine epsilon is not mentioned in the standard but is used to determine the upper bound on the relative error due to rounding. The machine epsilon for a single precision number is  $\epsilon = 2^{-24} \approx 5.96046*10^{-8}$ . This is the relative error. To determine the relative error the exponent value is set to zero. The number of significant bits in this case is 23 but the hidden bit increases this to 24 bits. Figure 2.6 and 2.5 illustrate the effect of the ULP. Both figures plot exactly the same number of points but in a different range. In Figure 2.5 from 10.000.000 to 10.000.010 and in Figure 2.6 in the range from 0 to 10. Ideally, both these lines should be straight to create the closest approximation to  $\mathbb R$ . We already know that this is not possible but the effects here make this explicitly clear. In Figure 2.5, the ULP represents a 1, while in Figure 2.6 it equals to approximately  $8.9*10^{-16}$ . The effects are clear: there is a trade-off in the precision and exponent size in floating point numbers. Consequently, problems may occur when using a number with a large exponent together with a small exponent number in the same mathematical operation, such as subtraction.

As already mentioned quantization introduces errors. To reduce the errors the IEEE-754 standard defines several rounding algorithms. The most popular is "rounding towards nearest, ties to even". This rounds towards the nearest value, if the number falls midway, it is rounded to the nearest even value. This mode

Figure 2.6 – Float curve limitation  $ULP \approx 8.9 * 10^{-16}$

generally introduces the smallest error with arithmetic operations. There are four more rounding modes, depicted in Table 2.5. These modes are not always available in hardware or made easily available to the programmer. For example on most Intel architectures they are only available via the Rounding Control field (RC) in the x87 FPU control register (bits 10,11) and MXCSR register (bits 13,14) [Intel, 2011]. Also, the Intel architectures do not offer the "Round toward nearest, ties away from zero option", since this was added in a later version of the standard. Setting the FPU control and MXCSR register bits to other values than the default values affects the performance of the architecture, for example the pipeline flushing, which is also a reason it is not done often.

DSP manufacturers will often make statements about full IEEE-754 compliancy. Even when the hardware is fully compliant to the IEEE-754 standard, it does not necessarily mean that everything that the standard describes has been implemented. After closer inspection of the datasheet, one will conclude that multiplication, addition and some boolean logic is supported in hardware. Often this does not include all of the rounding modes. There is a logical explanation for this. In most signal processing algorithms, the most common operations are multiplication, addition and comparison. Other operations can be constructed from these operations in software. Next to that, most software developers are not aware or care about the different rounding possibilities and will use the default one, "round to nearest ties to even". Support for subnormal numbers is often omitted by DSP manufacturers. Lacking this feature makes computation less complex and the processing elements will occupy less resources. Subnormal numbers are often defaulted to zero.

The implementation of the IEE-754 floating point format in hardware requires a lot of hardware resources, area and power, compared to fixed point. This is not entirely surprising since the mathematical operations require dif-

| Mode                                      | Description                                                                                                                                                            |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Round toward nearest, ties to even        | Rounds toward the nearest value, if<br>the number falls midway it is<br>rounded to the nearest even value (<br>LSB of 0)                                               |

| Round toward nearest, ties away from zero | Rounds to the nearest value, if the number falls midway it is rounded to the nearest larger value (for positive numbers) or nearest smaller one (for negative numbers) |

| Round toward 0                            | Rounds toward zero (i.e.,                                                                                                                                              |

truncation)

Rounds toward positive infinity

Rounds toward negative infinity

TABLE 2.5 – IEEE-754-2008 rounding modes

ferent hardware for the different parts of the floating point operands. Addition for example requires the operand to be aligned first, then the significands can be added together and afterwards the result needs to be normalized again. Combined with updating the exponent to the correct value as well as rounding correctly increases the required resources significantly.

#### 2.3 Conclusion

Round toward  $+\infty$

Round toward  $-\infty$

This chapter presented the most common number representations in current digital signal processors: integers, fixed-point, block floating-point, and floating-point. In practice, looking at common word lengths one finds often <1.15>, <1.31> in DSP devices. We have also shown block-floating point for cases where floating point is not available but where a larger range is desired. The main benefit of the block floating point format is the reduced amount of hardware resources compared to hardware floating point and still an increased available range compared to fixed point

We have shown that every representation has upsides and downsides and as such it is not always a clear-cut choice which representation to use. Based upon this chapter alone, one would most likely be most inclined to use as many bits as possible to get the best range an precision possible. In modern DSPs this would result in choosing IEEE-754 floating point or < 1.31 > fixed point if the range is limited. This is a fair choice but, unfortunately, precision and range are not the only factors for the choice for a number representation.

2.3 – Conclusion 21

From the information in this chapter, it is already clear that more precision means more bits and that floating point is more expensive than fixed-point. The next chapters will provide more insight in hardware and power penalties involved and the trade-offs that are possible.

# **Chapter 3**

# Payload processing

#### **Abstract**

Payload processing deals with the processing of instrument data on-board of a satellite. This instrument data consists of data coming from cameras or other sensors that need to be processed before it can be sent to Earth. Processing consists mainly of compressing data or reducing the data rate so it can be transmitted via a relatively low bandwidth channel. As a consequence of developments in sensor implementations, data rate needs to be reduced more and more because the accuracy of sensors increases more than the power and bandwidth available for the transmission channels. Reducing the data rate can be done by compressing the data or discarding data which is not of interest. This chapter deals with current processing platforms as well as an example of a platform intended for a future planned mission to the icy moons of Jupiter.

# 3.1 Current payloads

There are many satellite launches and missions. This chapter focuses on science missions managed by the European Space Agency, because part of the research was done in corporation with this agency.

Current payloads can roughly be divided in two categories regarding requirements: Earth orbiting platforms and missions that travel further into space. In Earth orbiting missions, the requirements are less strict regarding radiation and often there is a higher bandwidth available to send data back which directly influences the processing requirements. The radiation tolerance requirement influences the possibility to use different kinds of hardware and packaging. Closer to the earth, the hardware is shielded with the help of the earth's magnetic field and allows for hardware like SRAM-based FPGAs to be used which are more sensitive to radiation. This reduces costs since radiation-hardened ASICs are

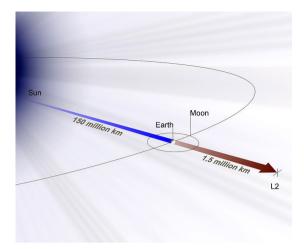

FIGURE 3.1 - Lagrangian point 2, Image Source: NASA

not widely available and the costs for new ASIC development is high, especially when qualified for deep space.

#### **3.2 ITAR**

Although politics should not be an issue in doing research, it unfortunately does play a role here. The processing elements that are described in the following sections might seem a bit odd to the observant reader. Why is there no Intel, TI, IBM or any other large silicon vendor on the list? This has to do with the export regulations to be observed by the USA, where most of these companies reside. In so-called International Traffic in Arms Regulations (ITAR) which makes it really difficult to export designs to be placed on satellites. Therefore companies that reside in Europe are the preferred choice for ESA to acquire processing elements.

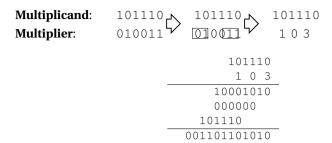

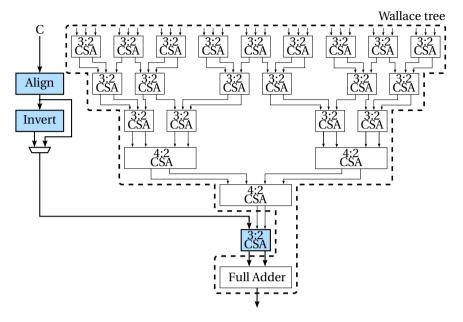

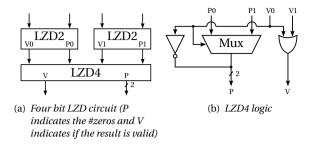

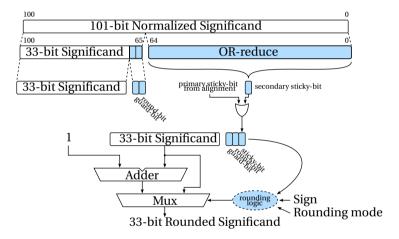

#### 3.3 Gaia